## **EAST-ADL** Introduction

EAST-ADL Requirements, Constraints and Verification & Validation

## Requirements introduction

Requirements express conditions or capabilities that must be met or possessed by a system or system component to satisfy a contract, standard, specification or other formally imposed properties.

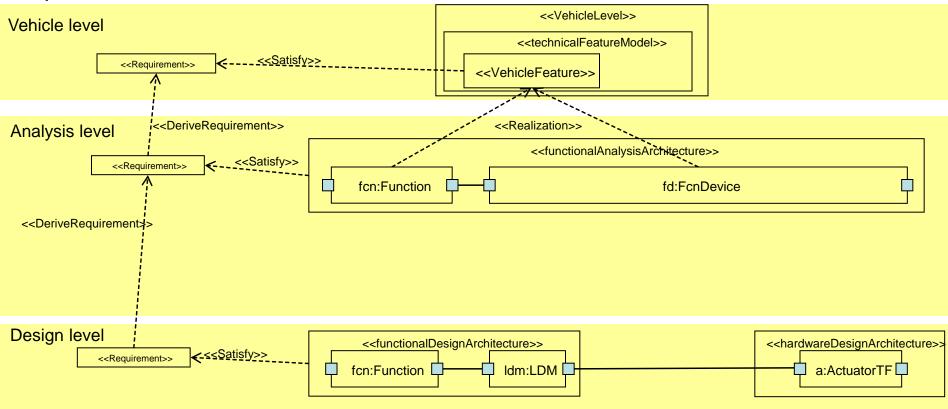

#### Requirements and Architecture

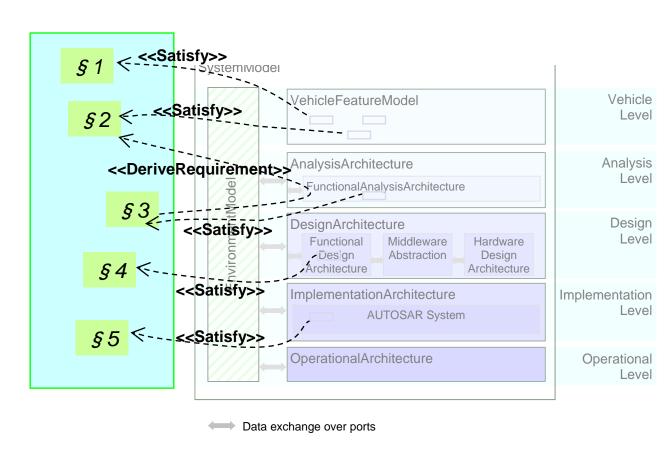

- The core EAST-ADL model captures basic structure of system

- Requirement elements annotate model to identify mandatory aspects

- Requirement elements relate requirements engineering information to architectural model

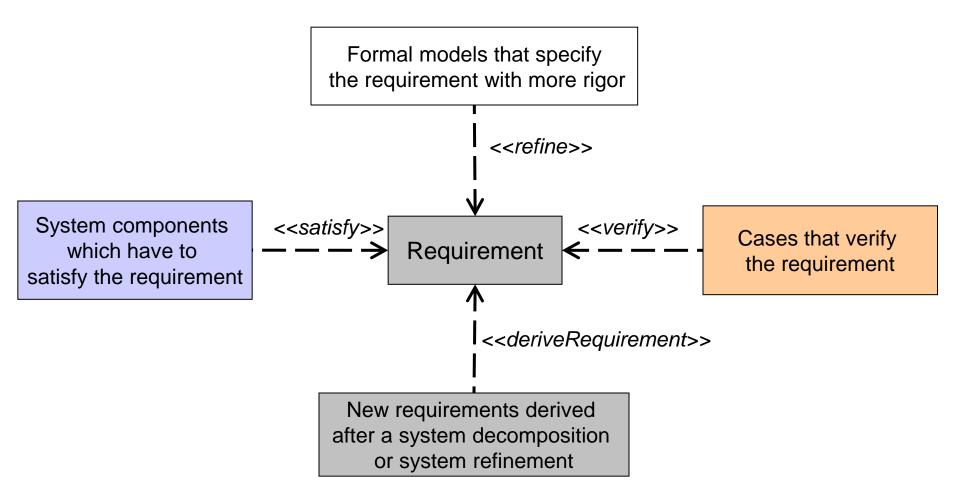

#### Requirements – basic relations

EAST-ADL Introduction: Requirements

## Requirements

Requirements are normally defined in a central repository.

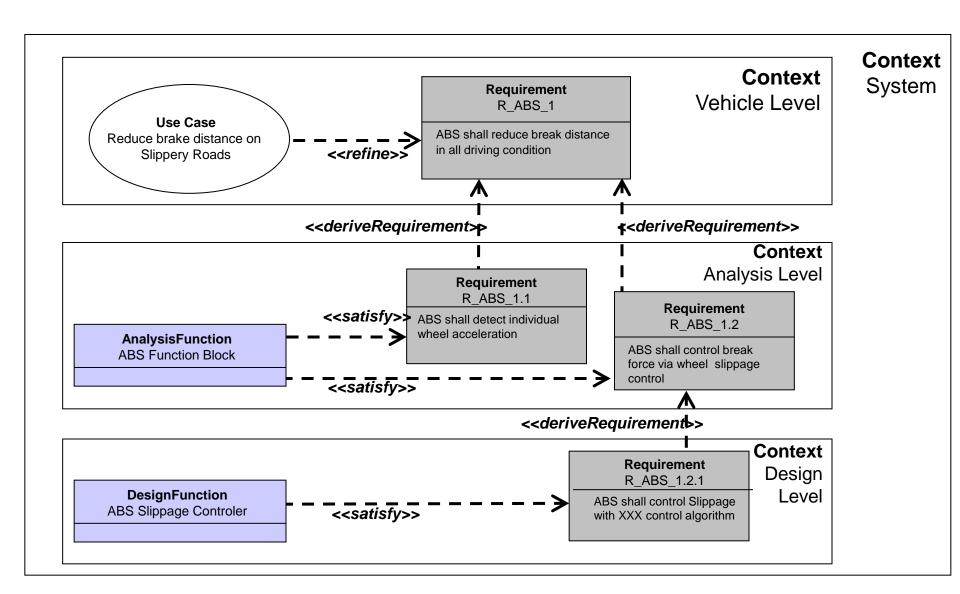

Satisfy relates requirements to features, functions and components.

Derive relates a derived requirement to its original.

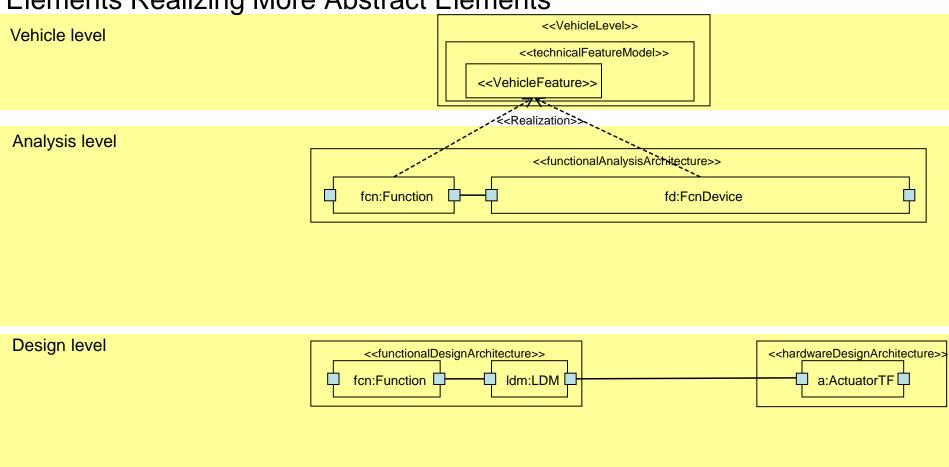

**Elements Realizing More Abstract Elements**

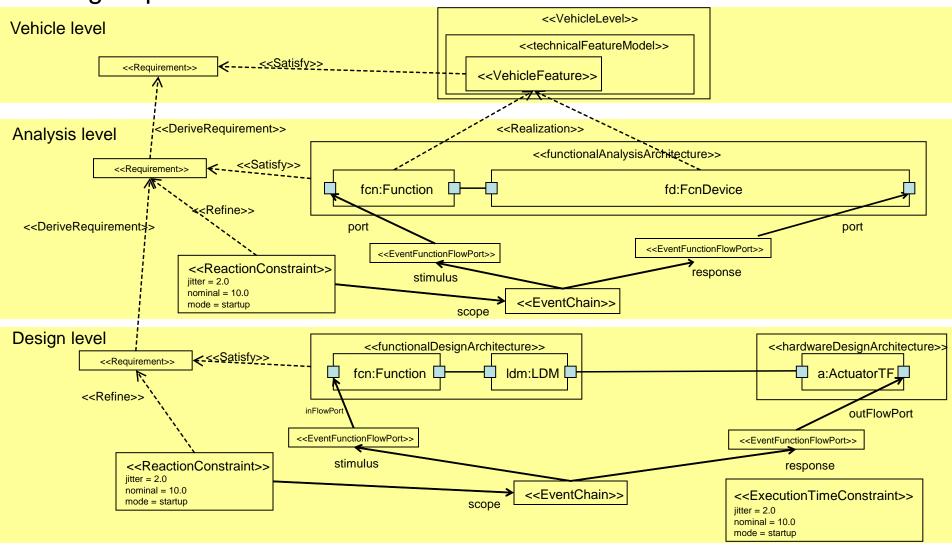

#### Requirements associated to elements and between abstraction levels

#### Refining requirements with formalized constraints

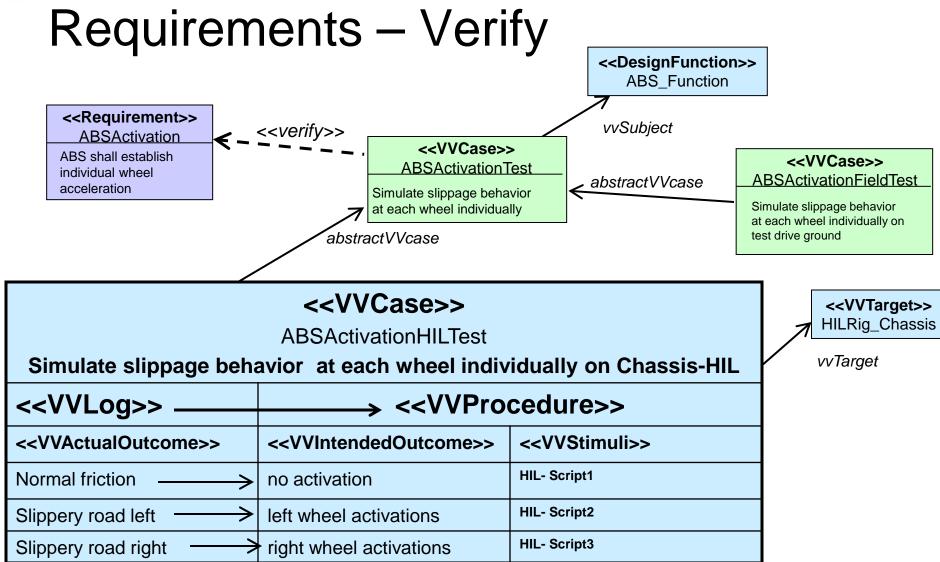

# Verification & validation support — basic concepts

- VVCase = a certain, overall V&V effort of varying scope and intention

- core concept of V&V support in EAST-ADL

- Safety analysis; specification, design or implementation review; analysis or design level simulation, SIL-testing, HIL-testing, vehicle testing

- VVProcedure = individual task in the context of an overall V&V effort (i.e. a VVCase), which has to be performed in order to achieve that effort's overall objective.

- VVTarget = concrete testing environment in/on which a particular V&V activity (i.e. VVProcedure) can be performed

- can be physical hardware or pure software (e.g. design level simulations)

- VVLog = captures outcome of an actual execution of a V&V activity

# Summary

- Requirement elements are textual (but may use a formal notation)

- Requirements are linked to architectural elements

- Requirements are linked to derived requirements

- Formalizations can be linked to requirements (Constraints and behavioural models)

- Requirements are linked to V&V constructs

- V&V constructs represent test cases and test results